This page was created by Trong-Thuc Hoang.

The page first is for my self-study, second is for helping newcomers to computer science.

(Assistant Professor) The University of Electro-Communications (UEC), Tokyo, Japan.

UEC website: linkContact:

(UEC)

(personal)

hoangtt@uec.ac.jp

trongthuc.hoang@gmail.com

Biography

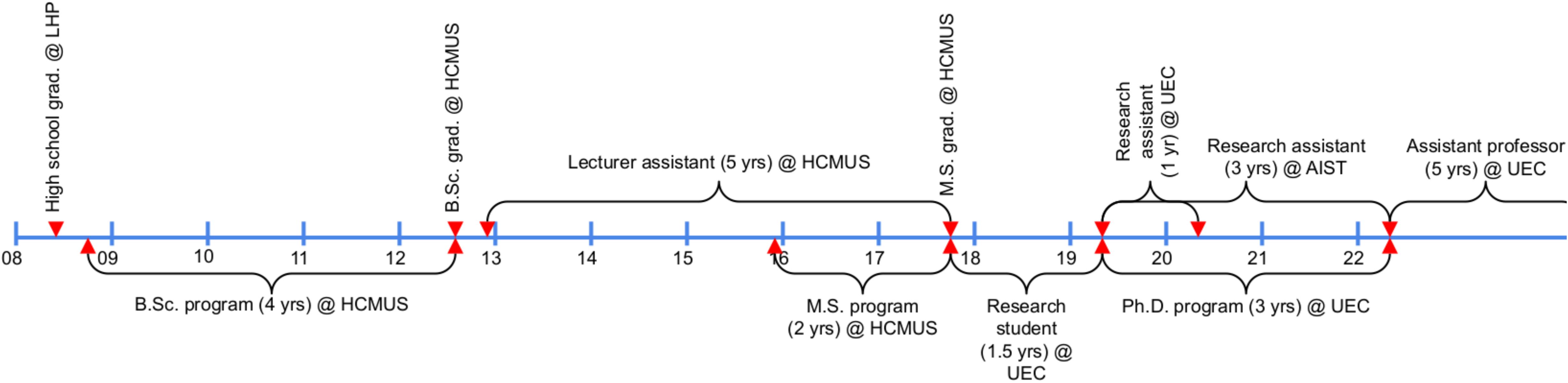

Trong-Thuc Hoang received a B.Sc. degree and an M.S. degree in Electronic Engineering from the University of Science (HCMUS), Hochiminh city, Vietnam, in 2012 and 2017, respectively. In 2022, he graduated from the University of Electro-Communications (UEC), Tokyo, Japan, with a Ph.D. degree in Engineering. From 2012 to 2017, he was a lecturer assistant at HCMUS. From 2019 to 2020, he was a research assistant at UEC. From 2019 to 2022, he was a research assistant at the Cyber-Physical Security Research Center (CPSEC), National Institute of Advanced Industrial Science and Technology (AIST), Tokyo, Japan. Since April of 2022, he has been an assistant professor at the Department of Computer and Network Engineering, UEC, Tokyo, Japan. His research interest mainly focuses on digital signal processing, computer architecture, cyber-security, ultra-low power circuit, and system-on-chip.

Publication

Journal (J): 48. Conference (C): 67. Other (O): 7. Total (J+C): 115

[ORCID] [Scopus] [Researchmap]

2025

Trong-Hung Nguyen, Duc-Thuan Dam, Phuc-Phan Duong, Tuan-Kiet Dang, Trong-Thuc Hoang, and Cong-Kha Pham, "A Timing-Constrained Design Methodology for Radix- 2k NTT in Polynomial Arithmetic," in IEEE Trans. on Circ. and Syst. I: Regular Papers (TCAS-I), vol. 72, no. 12, pp. 7794-7807, Dec. 2025. [DOI]

Tuan-Kiet Dang, Khai-Duy Nguyen, Trong-Thuc Hoang, and Cong-Kha Pham, "A Unified Approach to Strong PUF and TRNG Using Ring Generator for Cryptography," in IEEE Internet of Things Journal, vol. 12, no. 17, pp. 36590-36603, Sep. 2025. [DOI]

Tuan-Kiet Dang, Khai-Duy Nguyen, Trong-Thuc Hoang, and Cong-Kha Pham, "Dual-Mode PUF and TRNG Design with Ring Generator on 180nm CMOS," in Proc. of Int. Conf. on IC Design and Tech. (ICICDT), Lecce, Italy, Jun. 2025, pp. 41-44. [DOI]

Trong-Hung Nguyen, Tuan-Kiet Dang, Duc-Thuan Dam, Khai-Duy Nguyen, Phuc-Phan Duong, Cong-Kha Pham, and Trong-Thuc Hoang, "An Area-Time Efficient Hardware Architecture for ML-KEM Post-Quantum Cryptography Standard," in IEEE Access, vol. 13, pp. 103834-103847, Jun. 2025. [DOI]

Thai-Ha Tran, Duc-Thuan Dam, Van-Phuc Hoang, Trong-Thuc Hoang, and Cong-Kha Pham, "Enhanced Tower Field Mask Scheme with Affine Transformation-based Dynamic S-box," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), London, UK, May 2025, pp. 1-5. [DOI]

Duc-Thuan Dam, Thai-Ha Tran, Trong-Hung Nguyen, Trong-Thuc Hoang, and Cong-Kha Pham, "Compact FALCON FFT/NTT Accelerator for Post-Quantum Cryptography," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), London, UK, May 2025, pp. 1-5. [DOI]

Trong-Hung Nguyen, Duc-Thuan Dam, Phuc-Phan Duong, Trong-Thuc Hoang, and Cong-Kha Pham, "A Low-Latency Polynomial Arithmetic Unit for ML-KEM and ML-DSA Standards," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), London, UK, May 2025, pp. 1-5. [DOI]

Khai-Duy Nguyen, Tuan-Kiet Dang, Binh Kieu-Do-Nguyen, Cong-Kha Pham, and Trong-Thuc Hoang, "Live Demonstration: ASIC Implementation of ASCON Lightweight Cryptography for IoT Applications," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), London, UK, May 2025, pp. 1-1. [DOI]

Phuc-Phan Duong, Tuan-Kiet Dang, Trong-Thuc Hoang, and Cong-Kha Pham, "Compact 8-Bit S-Boxes Based on Multiplication in a Galois Field GF(24)," in Cryptography, vol. 9, no. 2, pp. 1-21, Apr. 2025. [DOI]

Chalumpol Trararak, Trong-Thuc Hoang, and Cong-Kha Pham, "Pedestrian Avoidance Simulation by Deep Reinforcement Learning Using Webots," in Proc. of Int. Conf. on Artificial Intelligence in Info. and Comm. (ICAIIC), Fukuoka, Japan, Feb. 2025, pp. 0734-0739. [DOI]

Trong-Hung Nguyen, Duc-Thuan Dam, Phuc-Phan Duong, Binh Kieu-Do-Nguyen, Cong-Kha Pham, and Trong-Thuc Hoang, "Efficient Hardware Implementation of the Lightweight CRYSTALS-Kyber," in IEEE Trans. on Circ. and Syst. I: Regular Papers (TCAS-I), vol. 72, no. 2, pp. 610-622, Feb. 2025. [DOI]

2024

Nhu-Hoang Nguyen, Tan-Phat Dang, Tuan-Kiet Tran, Thanh-Dat Bui, Trong-Thuc Hoang, and Huu-Thuan Huynh, "A Configurable 2D-Integer DCT Hardware Accelerator Compatible with H.266 Standard based on RISC-V Architecture," in Proc. of Int. Seminar on Research of Info. Tech. and Intelligent Syst. (ISRITI), Yogyakarta, Indonesia, Dec. 2024, pp. 894-899. [DOI]

Tuan-Kiet Dang, Trong-Thuc Hoang, Cong-Kha Pham, "A True Random Number Generator on FPGA with Jitter-Sampling by Ring Generator," in Asian Hardware Oriented Secu. and Trust Symp. (AsianHOST), Kobe, Japan, Dec. 2024, pp. 1-6. [DOI]

Trong-Hung Nguyen, Duc-Thuan Dam, Phuc-Phan Duong, Cong-Kha Pham, and Trong-Thuc Hoang, "A Compact SHA3 Implementation for Post-Quantum Cryptography," in Proc. of Int. Conf. on Crypto. and Info. Secu. (VCRIS), Hanoi, Vietnam, Dec. 2024, pp. 1-5. [DOI]

Phuc-Phan Duong, Ba-Anh Dao, Thai-Ha Tran, Trong-Hung Nguyen, Trong-Thuc Hoang, and Cong-Kha Pham, "Resource-Efficient 4×4 S-Boxes Using Chaotic Map," in Proc. of Int. Conf. on Crypto. and Info. Secu. (VCRIS), Hanoi, Vietnam, Dec. 2024, pp. 1-6. [DOI]

Thai-Ha Tran, Duc-Thuan Dam, Binh Kieu-Do-Nguyen, Van-Phuc Hoang, Trong-Thuc Hoang, and Cong-Kha Pham, "Hardware Implementation of a Hybrid Dynamic Gold Code-Based Countermeasure Against Side-Channel Attacks," in Proc. of Annual Int. Conf. on Privacy, Security and Trust (PST), Sydney, Australia, Aug. 2024, pp. 1-5. [DOI]

Duc-Thuan Dam, Trong-Hung Nguyen, Thai-Ha Tran, Binh Kieu-Do-Nguyen, Trong-Thuc Hoang, and Cong-Kha Pham, "An Efficient Method for Accelerating Kyber and Dilithium Post-Quantum Cryptography," in Proc. of Annual Int. Conf. on Privacy, Security and Trust (PST), Sydney, Australia, Aug. 2024, pp. 1-5. [DOI]

Thai-Ha Tran, Ba-Anh Dao, Duc-Hung Le, Van-Phuc Hoang, Trong-Thuc Hoang, and Cong-Kha Pham, "Spread Spectrum-Based Countermeasures for Cryptographic RISC-V SoC," in IEEE Trans. on Very Large Scale Integration (VLSI) Syst., vol. 32, no. 12, pp. 2341-2354, Aug. 2024. [DOI]

Binh Kieu-Do-Nguyen, Khai-Duy Nguyen, Nguyen The Binh, Tuan-Kiet Dang, Duc-Hung Le, Cuong Pham-Quoc, Ngoc-Thinh Tran, Cong-Kha Pham, and Trong-Thuc Hoang, "A Resource-Efficient Multi-core Multi-thread RISC-V-based System-on-Chip," in Proc. of Int. SoC Design Conf. (ISOCC), Sapporo, Japan, Aug. 2024, pp. 310-311. [DOI]

Binh Kieu-Do-Nguyen, Khai-Duy Nguyen, Tuan-Kiet Dang, Cong-Kha Pham, and Trong-Thuc Hoang, "A Trusted Execution Environment RISC-V System on Chip," in Proc. of IEEE Hot Chips Symp. (HCS), Stanford, CA, USA, Aug. 2024, pp. 1-1. [DOI]

Khai-Duy Nguyen, Tuan-Kiet Dang, Binh Kieu-Do-Nguyen, Cong-Kha Pham, and Trong-Thuc Hoang, "RISC-V-Based System-on-Chips for IoT Applications," in Proc. of IEEE Hot Chips Symp. (HCS), Stanford, CA, USA, Aug. 2024, pp. 1-1. [DOI]

Nhu-Hoang Nguyen, Tan-Phat Dang, Thanh-Dat Bui, Trong-Thuc Hoang, Cong-Kha Pham, and Huu-Thuan Huynh, "Designing and Implementing a 2D Integer DCT Hardware Accelerator Fully Compatible with Versatile Video Coding," in Proc. of Comp. Science and Its Appl. (ICCSA), Hanoi, Vietnam, Jul. 2024, pp. 110-121. [DOI]

Binh Kieu-Do-Nguyen, Nguyen The Binh, Cuong Pham-Quoc, Huynh Phuc Nghi, Ngoc-Thinh Tran, Trong-Thuc Hoang, and Cong-Kha Pham, "Compact and Low-Latency FPGA-Based Number Theoretic Transform Architecture for CRYSTALS Kyber Postquantum Cryptography Scheme," in Information, vol. 15, no. 7, pp. 1-15, Jul. 2024. [DOI]

Duc-Thuan Dam, Trong-Hung Nguyen, Binh Kieu-Do-Nguyen, Trong-Thuc Hoang, and Cong-Kha Pham, "RISC-V SoC with NTT-Blackbox for CRYSTALS-Kyber Post-Quantum Cryptography," in Proc. of Int. Conf. on Integrated Circ., Design, and Veri. (ICDV), Hanoi, Vietnam, Jun. 2024, pp. 49-54. [DOI]

Phuc-Phan Duong, Hieu Minh Nguyen, Ba-Anh Dao, Thai-Ha Tran, Binh Kieu-Do-Nguyen, Cong-Kha Pham, and Trong-Thuc Hoang, "S-Boxes with Optimal Strict Avalanche Criterion using Chaotic Map," in Proc. of Int. Conf. on Integrated Circ., Design, and Veri. (ICDV), Hanoi, Vietnam, Jun. 2024, pp. 85-90. [DOI]

Binh Kieu-Do-Nguyen, Khai-Duy Nguyen, Tuan-Kiet Dang, Nguyen The Binh, Cuong Pham-Quoc, Ngoc-Thinh Tran, Cong-Kha Pham, and Trong-Thuc Hoang, "A Trusted Execution Environment RISC-V System-on-Chip Compatible with Transport Layer Security 1.3," in Electronics, vol. 13, no. 13, pp. 1-24, Jun. 2024. [DOI]

Trong-Thuc Hoang, Binh Kieu-Do-Nguyen, and Cong-Kha Pham, "Secured Network-on-Chip Framework for RISC-V Computing Systems," Keynote in Int. Conf. on Integrated Circ., Design, and Veri. (ICDV), Hanoi, Vietnam, Jun. 2024. [PDF]

Trong-Hung Nguyen, Nguyen The Binh, Huynh Phuc Nghi, Cong-Kha Pham, and Trong-Thuc Hoang, "Unified-pipelined NTT Architecture for Polynomial Multiplication in Lattice-based Cryptosystems," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Singapore, May 2024, pp. 1-5. [DOI]

Phuc-Phan Duong, Trong-Thuc Hoang, and Cong-Kha Pham, "A Strong 4 × 4 S-Box Using an Enhanced Tent Map," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Singapore, May 2024, pp. 1-5. [DOI]

Thai-Ha Tran, Van-Phuc Hoang, Duc-Hung Le, Trong-Thuc Hoang, and Cong-Kha Pham, "An Efficient Hiding Countermeasure with Xilinx MMCM Primitive in Spread Mode," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Singapore, May 2024, pp. 1-5. [DOI]

Ronaldo Serrano, Ckristian Duran, Marco Sarmiento, Khai-Duy Nguyen, Tetsuya Iizuka, Trong-Thuc Hoang, and Cong-Kha Pham, "A Unified OTP and PUF Exploiting Post-Program Current on Standard CMOS Technology," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Singapore, May 2024, pp. 1-5. [DOI]

Binh Kieu-Do-Nguyen, Tuan-Kiet Dang, Nguyen The Binh, Cuong Pham-Quoc, Huynh Phuc Nghi, Ngoc-Thinh Tran, Katsumi Inoue, Cong-Kha Pham, and Trong-Thuc Hoang, "A High-Performance Non-Indexed Text Search System," in Electronics, vol. 13, no. 11, pp. 1-21, May 2024. [DOI]

Ta Viet Tai, Ma Pham Nhut Tan, Duong Hoang Tien, Nguyen Viet Ha, Trong-Thuc Hoang, Cong-Kha Pham, and Tran Thi Thao Nguyen, "A Novel ECG Signal Quality Index Method Based on Skewness-MODWT Analysis," in IEEE Access, vol. 12, pp. 70184-70197, May 2024. [DOI]

Phuc-Phan Duong, Hieu Minh Nguyen, Ba-Anh Dao, Binh Kieu-Do-Nguyen, Thai-Ha Tran, Trong-Thuc Hoang, and Cong-Kha Pham, "Construction of Robust Lightweight S-Boxes Using Enhanced Logistic and Enhanced Sine Maps," in IEEE Access, vol. 12, pp. 63976-63994, May 2024. [DOI]

Tuan-Kiet Dang, Khai-Duy Nguyen, Binh Kieu-Do-Nguyen, Trong-Thuc Hoang, and Cong-Kha Pham, "Realization of Authenticated One-Pass Key Establishment on RISC-V Micro-Controller for IoT Applications," in Future Internet, vol. 16, no. 5, pp. 1-17, May 2024. [DOI]

Huu-Thuan Huynh, Tan-Phat Dang, Tuan-Kiet Tran, Trong-Thuc Hoang, and Cong-Kha Pham, "A Multimode SHA-3 Accelerator Based on RISC-V System," in IEICE Elec. Express (ELEX), vol. 21, no. 11, pp. 20240156-20240156, Apr. 2024. [DOI]

Tuan-Kiet Dang, Khai-Duy Nguyen, Cong-Kha Pham, and Trong-Thuc Hoang, "Accumulator-Based 16-Bit Processor for Wireless Sensor Nodes," in IEEE Trans. on Circ. and Syst. II: Express Briefs (TCAS-II), vol. 71, no. 7, pp. 3543-3547, Feb. 2024. [DOI]

Trong-Hung Nguyen, Binh Kieu-Do-Nguyen, Cong-Kha Pham, and Trong-Thuc Hoang, "High-Speed NTT Accelerator for CRYSTAL-Kyber and CRYSTAL-Dilithium," in IEEE Access, vol. 12, pp. 34918-34930, Feb. 2024. [DOI]

2023

Thai-Ha Tran, Duc-Thuan Dam, Ba-Anh Dao, Van-Phuc Hoang, Cong-Kha Pham, and Trong-Thuc Hoang, "Compacting Side-Channel Measurements With Amplitude Peak Location Algorithm," in IEEE Trans. on Very Large Scale Integration (VLSI) Syst., vol. 32, no. 3, pp. 573-586, Dec. 2023. [DOI]

Nguyen The Binh, Binh Kieu-Do-Nguyen, Trong-Thuc Hoang, Cong-Kha Pham, and Cuong Pham-Quoc, "FPGA-Based Secured and Efficient Lightweight IoT Edge Devices with Customized RISC-V," in Proc. of Int. Conf. on Comp. and Comm. Techn. (RIVF), Hanoi, Vietnam, Dec. 2023, pp. 31-36. [DOI]

Van-Phuc Hoang, Ngoc-Tuan Do, Trong-Thuc Hoang, and Cong-Kha Pham, "Revealing Secret Key from Low Success Rate Deep Learning-Based Side Channel Attacks," in Proc. of IEEE Int. Symp. on Embedded Multicore/Many-core Syst.-on-Chip (MCSoC), Singapore, Dec. 2023, pp. 9-14. [DOI]

Huu-Thuan Huynh, Tan-Phat Dang, Trong-Thuc Hoang, Cong-Kha Pham, and Tuan-Kiet Tran, "An Efficient Cryptographic Accelerators for IoT System Based on Elliptic Curve Digital Signature," in Proc. of Intelligent Systems and Data Science (ISDS), Can Tho, Vietnam, Nov. 2023, pp. 106-118. [DOI]

Tan-Phat Dang, Tuan-Kiet Tran, Trong-Thuc Hoang, Cong-Kha Pham, and Huu-Thuan Huynh, "The Efficiency of High-performance SHA-3 Accelerator on the System Level," in Proc. of Int. Symp. on Electrical and Electronics Engi. (ISEE), Hochiminh city, Vietnam, Oct. 2023, pp. 7-12. [DOI]

Trong-Hung Nguyen, Cong-Kha Pham, and Trong-Thuc Hoang, "A High-Speed Barret-Based Modular Multiplication with Bit-Correction for the CRYSTAL-KYBER Cryptosystem," in Proc. of Intelligence of Things: Tech. and Appl. (ICIT), Hochiminh city, Vietnam, Oct. 2023, pp. 191-199. [DOI]

Tan-Phat Dang, Tuan-Kiet Tran, Trong-Thuc Hoang, Cong-Kha Pham, and Huu-Thuan Huynh, "A High-Performance Pipelined FPGA-SoC Implementation of SHA3-512 for Single and Multiple Message Blocks," in Proc. of Intelligence of Things: Tech. and Appl. (ICIT), Hochiminh city, Vietnam, Oct. 2023, pp. 288-298. [DOI]

Tuan-Kiet Tran, Tan-Phat Dang, Trong-Thuc Hoang, Cong-Kha Pham, and Huu-Thuan Huynh, "Optimizing ECC Implementations Based on SoC-FPGA with Hardware Scheduling and Full Pipeline Multiplier for IoT Platforms," in Proc. of Intelligence of Things: Tech. and Appl. (ICIT), Hochiminh city, Vietnam, Oct. 2023, pp. 299-309. [DOI]

Trong-Thuc Hoang and Cong-Kha Pham, "RISC-V Trusted Platform Module (TPM) and Trusted Execution Environment (TEE)," Keynote in Symp. on Comp. Science and Engi. (SCSE), Hochiminh city, Vietnam, Oct. 2023. [PDF]

Trong-Hung Nguyen, Cong-Kha Pham, and Trong-Thuc Hoang, "A High-Efficiency Modular Multiplication Digital Signal Processing for Lattice-Based Post-Quantum Cryptography," in Cryptography, vol. 7, no. 4, pp. 1-17, Sep. 2023. [DOI]

Duc-Thuan Dam, Thai-Ha Tran, Van-Phuc Hoang, Cong-Kha Pham, and Trong-Thuc Hoang, "A Survey of Post-Quantum Cryptography: Start of a New Race," in Cryptography, vol. 7, no. 3, pp. 1-18, Aug. 2023. [DOI]

Thai-Ha Tran, Anh-Tien Le, Trong-Thuc Hoang, Van-Phuc Hoang, and Cong-Kha Pham, "Dynamic Gold Code-Based Chaotic Clock for Cryptographic Designs to Counter Power Analysis Attacks," in Proc. of the Great Lakes Symp. on VLSI (GLVLSI), Knoxville, TN, USA, Jun. 2023, pp. 439-442. [DOI]

Ronaldo Serrano, Marco Sarmiento, Ckristian Duran, Tuan-Kiet Dang, Trong-Thuc Hoang, and Cong-Kha Pham, "In-NVRAM Unified PUF and TRNG Based on Standard CMOS Technology," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Monterey, CA, USA, May 2023, pp. 1-5. [DOI]

Thai-Ha Tran, Ba-Anh Dao, Trong-Thuc Hoang, Van-Phuc Hoang, and Cong-Kha Pham, "Transition Factors of Power Consumption Models for CPA Attacks on Cryptographic RISC-V SoC," in IEEE Trans. on Comp., vol. 72, no. 9, pp. 2689-2700, Mar. 2023. [DOI]

Binh Kieu Do-Nguyen, Cuong Pham-Quoc, Ngoc-Thinh Tran, Cong-Kha Pham, and Trong-Thuc Hoang, "Multi-Functional Resource-Constrained Elliptic Curve Cryptographic Processor," in IEEE Access, vol. 11, pp. 4879-4894, Jan. 2023. [DOI]

Anh-Tien Le, Trong-Thuc Hoang, Ba-Anh Dao, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "A Cross-process Spectre Attack via Cache on RISC-V Processor with Trusted Execution Environment," in Comp. and Elec. Engi., vol. 105, no. 1, pp. 108546, Jan. 2023. [DOI]

2022

Trong-Thuc Hoang, "Ultra-Low-Power (ULP) System-on-Chip (SoC) for Internet-of-Things (IoT) Edge Computing," in Proc. of Vietnamese Academic Network in Japan (VANJ), Tokyo, Japan, Nov. 2022. [PDF]

Tuan-Kiet Dang, Ronaldo Serrano, Trong-Thuc Hoang, and Cong-Kha Pham, "A Novel Ring Oscillator PUF for FPGA Based on Feedforward Ring Oscillators," in Proc. of Int. SoC Design Conf. (ISOCC), Gangneung-si, South Korea, Oct. 2022, pp. 87-88. [DOI]

Ronaldo Serrano, Marco Sarmiento, Ckristian Duran, Trong-Thuc Hoang, and Cong-Kha Pham, "A 3.65 Gb/s Area-Efficiency ChaCha20 Cryptocore," in Proc. of Int. SoC Design Conf. (ISOCC), Gangneung-si, South Korea, Oct. 2022, pp. 79-80. [DOI]

Ronaldo Serrano, Ckristian Duran, Marco Sarmiento, Tuan-Kiet Dang, Trong-Thuc Hoang, and Cong-Kha Pham, "A Unified PUF and Crypto Core Exploiting the Metastability in Latches," in Future Internet, vol. 14, no. 10, pp. 1-12, Oct. 2022. [DOI]

Trong-Thuc Hoang, Ba-Anh Dao, Anh-Tien Le, Van-Phuc Hoang, and Cong-Kha Pham, "Tutorial: RISC-V Computer System Designed for Cyber-Security," in Proc. of Int. Conf. on IC Design and Tech. (ICICDT), Hanoi, Vietnam, Sep. 2022. [PDF]

Binh Kieu-Do-Nguyen, Dang Tuan Kiet, Trong-Thuc Hoang, Katsumi Inoue, Toshinori Usugi, Masanori Odaka, Shuichi Kameyama, and Cong-Kha Pham, "High-speed FPGA-based Design and Implementation of Text Search Processor," in Proc. of Int. Conf. on IC Design and Tech. (ICICDT), Hanoi, Vietnam, Sep. 2022, pp. 109-112. [DOI]

Dang Tuan Kiet, Khai-Duy Nguyen, Nguyen Quang Nhu Quynh, Trong-Thuc Hoang, and Cong-Kha Pham, "A System-on-Chip for IoT Applications with 16-bit Tiny Processor," in Proc. of Int. Conf. on IC Design and Tech. (ICICDT), Hanoi, Vietnam, Sep. 2022, pp. 44-47. [DOI]

Binh Kieu-Do-Nguyen, Trong-Thuc Hoang, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "High-performance Multi-function HMAC-SHA2 FPGA Implementation," in Proc. of IEEE Int. NEWCAS Conf. (NEWCAS), Quebec City, QC, Canada, Jun. 2022, pp. 30-34. [DOI]

Serrano Ronaldo, Ckristian Duran, Marco Sarmiento, Cong-Kha Pham, and Trong-Thuc Hoang, "ChaCha20–Poly1305 Authenticated Encryption with Additional Data for Transport Layer Security 1.3," in Cryptography, vol. 6, no. 2, pp. 1-12, Jun. 2022. [DOI]

Anh-Tien Le, Trong-Thuc Hoang, Ba-Anh Dao, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "Spectre Attack Detection with Neutral Network on RISC-V Processor," in Proc. of Int. Symp. on Circ. and Syst. (ISCAS), Austin, TX, USA, May 2022, pp. 2467-2471. [DOI]

Binh Kieu-Do-Nguyen, Cuong Pham-Quoc, Ngoc-Thinh Tran, Cong-Kha Pham, and Trong-Thuc Hoang, "Low-Cost Area-Efficient FPGA-Based Multi-Functional ECDSA/EdDSA," in Cryptography, vol. 6, no. 2, pp. 1-13, May 2022. [DOI]

Trong-Thuc Hoang, Ckristian Duran, Ronaldo Serrano, Marco Sarmiento, Khai-Duy Nguyen, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "Trusted Execution Environment Hardware by Isolated Heterogeneous Architecture for Key Scheduling," in IEEE Access, vol. 10, pp. 46014-46027, Apr. 2022. [DOI]

Ronaldo Serrano, Ckristian Duran, Marco Sarmiento, Trong-Thuc Hoang, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "A Robust and Healthy Against PVT Variations TRNG Based on Frequency Collapse," in IEEE Access, vol. 10, pp. 41852-41862, Apr. 2022. [DOI]

Marco Sarmiento, Khai-Duy Nguyen, Ckristian Duran, Ronaldo Serrano, Trong-Thuc Hoang, Koichiro Ishibashi, and Cong-Kha Pham, "Systems on a Chip With 8 and 32 Bits Processors in 0.18-μm Technology for IoT Applications," in IEEE Trans. on Circ. and Syst. II: Express Briefs (TCAS-II), vol. 69, no. 5, pp. 2438-2442, Mar. 2022. [DOI]

2021

Anh-Tien Le, Trong-Thuc Hoang, Ba-Anh Dao, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "A Real-Time Cache Side-Channel Attack Detection System on RISC-V Out-of-Order Processor," in IEEE Access, vol. 9, pp. 164597–164612, Dec. 2021. [DOI]

Ba-Anh Dao, Trong-Thuc Hoang, Anh-Tien Le, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "Correlation Power Analysis Attack Resisted Cryptographic RISC-V SoC With Random Dynamic Frequency Scaling Countermeasure," in IEEE Access, vol. 9, pp. 151993-152014, Nov. 2021. [DOI]

Ronaldo Serrano, Ckristian Duran, Trong-Thuc Hoang, Marco Sarmiento, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "ChaCha20-Poly1305 Crypto Core Compatible with Transport Layer Security 1.3," in Proc. of Int. SoC Design Conf. (ISOCC), Jeju Island, South Korea, Oct. 2021, pp. 17-18. [DOI]

Ronaldo Serrano, Marco Sarmiento, Ckristian Duran, Khai-Duy Nguyen, Trong-Thuc Hoang, Koichiro Ishibashi, and Cong-Kha Pham, "A Low-Power Low-Area SoC based in RISC-V Processor for IoT Applications," in Proc. of Int. SoC Design Conf. (ISOCC), Jeju Island, South Korea, Oct. 2021, pp. 375-376. [DOI]

Binh Kieu-Do-Nguyen, Trong-Thuc Hoang, Cong-Kha Pham, and Cuong Pham-Quoc, "A Power-efficient Implementation of SHA-256 Hash Function for Embedded Applications," in Proc. of Int. Conf. on Advanced Tech. for Comm. (ATC), Hochiminh city, Vietnam, Oct. 2021, pp. 39-44. [DOI]

Trong-Thuc Hoang, Ckristian Duran, Ronaldo Serrano, Marco Sarmiento, Khai-Duy Nguyen, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "System-on-Chip Implementation of Trusted Execution Environment with Heterogeneous Architecture," in Proc. of IEEE Hot Chips Symp. (HCS), Palo Alto, CA, USA, Aug. 2021, pp. 1-16. [DOI]

Khai-Duy Nguyen, Dang Tuan Kiet, Trong-Thuc Hoang, Nguyen Quang Nhu Quynh, and Cong-Kha Pham, "A CORDIC-based Trigonometric Hardware Accelerator with Custom Instruction in 32-bit RISC-V System-on-Chip," in Proc. of IEEE Hot Chips Symp. (HCS), Palo Alto, CA, USA, Aug. 2021, pp. 1-13. [DOI]

Khai-Duy Nguyen, Dang Tuan Kiet, Trong-Thuc Hoang, Nguyen Quang Nhu Quynh, Xuan-Tu Tran, and Cong-Kha Pham, "A Trigonometric Hardware Acceleration in 32-bit RISC-V Microcontroller with Custom Instruction," in IEICE Electronics Express (ELEX), vol. 18, no. 16, pp. 20210266, Aug. 2021. [DOI]

Dang Tuan Kiet, Binh Kieu-Do-Nguyen, Trong-Thuc Hoang, Khai-Duy Nguyen, Xuan-Tu Tran, and Cong-Kha Pham, "A Proposal for Enhancing Training Speed in Deep Learning Models Based on Memory Activity Survey," in IEICE Electronics Express (ELEX), vol. 18, no. 15, pp. 20210252, Aug. 2021. [DOI]

Ronaldo Serrano, Ckristian Duran, Trong-Thuc Hoang, Marco Sarmiento, Khai-Duy Nguyen, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "A Fully Digital True Random Number Generator with Entropy Source Based in Frequency Collapse," in IEEE Access, vol. 9, pp. 105748-105755, Jul. 2021. [DOI]

Marco Sarmiento, Khai-Duy Nguyen, Ckristian Duran, Trong-Thuc Hoang, Ronaldo Serrano, Van-Phuc Hoang, Xuan-Tu Tran, Ishibashi Koichiro, and Cong-Kha Pham, "A Sub-μW Reversed-Body-Bias 8-bit Processor on 65-nm Silicon-On-Thin-Box (SOTB) for IoT Applications," in IEEE Trans. on Circ. and Syst. II: Express Briefs (TCAS-II), vol. 68, no. 9, pp. 3182-3186, Jun. 2021. [DOI]

Ba-Anh Dao, Trong-Thuc Hoang, Anh-Tien Le, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "Exploiting the Back-Gate Biasing Technique as a Countermeasure Against Power Analysis Attacks," in IEEE Access, vol. 9, pp. 24768-24786, Feb. 2021. [DOI]

2020

Trong-Thuc Hoang, Ckristian Duran, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "Trusted Execution Environment (TEE) on Open-source RISC-V Processor System," in Proc. of Vietnamese Academic Network in Japan (VANJ), Tokyo, Japan, Nov. 2020. [PDF]

Trong-Thuc Hoang, Ckristian Duran, Khai-Duy Nguyen, Tuan-Kiet Dang, Quynh Nguyen Quang Nhu, Phuc-Hong Than, Xuan-Tu Tran, Duc-Hung Le, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "Low-power High-performance 32-bit RISC-V Microcontroller on 65-nm Silicon-On-Thin-BOX (SOTB)," in IEICE Electronics Express (ELEX), vol. 17, no. 20, pp. 20200282, Oct. 2020. [DOI]

Trong-Thuc Hoang, Ckristian Duran, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "Cryptographic Accelerators for Trusted Execution Environment in RISC-V Processor," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Seville, Spain, Oct. 2020, pp. 1-4. [DOI]

Trong-Thuc Hoang, Ckristian Duran, Duc-Thinh Nguyen-Hoang, Duc-Hung Le, Akira Tsukamoto, Kuniyasu Suzaki, and Cong-Kha Pham, "Quick Boot of Trusted Execution Environment with Hardware Accelerators," in IEEE Access, vol. 8, pp. 74015-74023, Apr. 2020. [DOI]

Xuan-Thuan Nguyen, Trong-Thuc Hoang, Hong-Thu Nguyen, Katsumi Inoue, and Cong-Kha Pham, "A 0.9-V 50-MHz 256-bit 1D-to-2D-based Single/Multi-match Priority Encoder with 0.67-nW Standby Power on 65-nm SOTB CMOS," in Microprocessors and Microsystems, vol. 73, pp. 102970, Mar. 2020. [DOI]

2019

Akinori Yamamoto, Trong-Thuc Hoang, and Cong-Kha Pham, "A Ring Oscillator Using Bootstrap Inverter," in Proc. of IEEE SOI-3D-Subthreshold Microelec. Tech. Unified Conf. (S3S), San Jose, California, USA, Oct. 2019, pp. 1-2. [DOI]

Ngoc-Tu Bui, Trong-Thuc Hoang, Akinori Yamamoto, Duc-Hung Le, and Cong-Kha Pham, "A 0.75-V 58-MHz 340-μW SOTB-65nm 32-point DCT Implementation Based on Fixed-rotation Adaptive CORDIC," in Proc. of IEEE SOI-3D-Subthreshold Microelec. Tech. Unified Conf. (S3S), San Jose, California, USA, Oct. 2019, pp. 1-3. [DOI]

Xuan-Thuan Nguyen, Trong-Thuc Hoang, Hong-Thu Nguyen, Katsumi Inoue, and Cong-Kha Pham, "A 1.2-V 162.9-pJ/cycle Bitmap Index Creation Core with 0.31-pW/bit Standby Power on 65-nm SOTB," in Microprocessors and Microsystems, vol. 69, pp. 112-117, Sep. 2019. [DOI]

Trong-Thuc Hoang, Xuan-Thuan Nguyen, Duc-Hung Le, and Cong-Kha Pham, "Low-Power Floating-Point Adaptive-CORDIC-Based FFT Twiddle Factor on 65-nm Silicon-on-Thin-BOX (SOTB) With Back-Gate Bias," in IEEE Trans. on Circ. and Syst. II: Express Briefs (TCAS-II), vol. 66, no. 10, pp. 1723-1727, Jul. 2019. [DOI]

Duc-Hung Le, Trong-Thuc Hoang, and Cong-Kha Pham, "A 1.05-V 62-MHz with 0.12-nW Standby Power SOTB-65nm Chip of 32-point DCT Based on Adaptive CORDIC," in IEICE Electronics Express (ELEX), vol. 16, no. 10, pp. 20190116, May 2019. [DOI]

Xuan-Thuan Nguyen, Trong-Thuc Hoang, Katsumi Inoue, Ngoc-Tu Bui, Van-Phuc Hoang, and Cong-Kha Pham, "A 1.2-V 90-MHz Bitmap Index Creation Accelerator with 0.27-nW Standby Power on 65-nm Silicon-On-Thin-Box (SOTB) CMOS," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Sapporo, Japan, May 2019, pp. 1-4. [DOI]

Takahiro Hosaka, Trong-Thuc Hoang, Van-Phuc Hoang, Duc-Hung Le, Katsumi Inoue, and Cong-Kha Pham, "Live Demonstration: Real-time Auto-exposure Histogram Equalization Video-system Using Frequent Items Counter," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Sapporo, Japan, May 2019, pp. 1-1. [DOI]

Xuan-Thuan Nguyen, Trong-Thuc Hoang, Hong-Thu Nguyen, Katsumi Inoue, and Cong-Kha Pham, "An Efficient I/O Architecture for RAM-based Content-Addressable Memory on FPGA," in IEEE Tran. on Circ. and Syst. II: Express Briefs (TCAS-II), vol. 66, no. 3, pp. 472-476, Mar. 2019. [DOI]

Ngoc-Tu Bui, Trong-Thuc Hoang, Duc-Hung Le, and Cong-Kha Pham, "A 0.75-V 32-MHz 181-μW SOTB-65nm Floating-point Twiddle Factor Using Adaptive CORDIC," in Proc. of IEEE Int. Conf. on Industrial Tech. (ICIT), Melbourne, Australia, Feb. 2019, pp. 835-840. [DOI]

2018

Katsumi Inoue, Trong-Thuc Hoang, and Cong-Kha Pham, "Frequent Items Counter Based on Binary Decoders," in IEICE Electronics Express (ELEX), vol. 15, no. 20, pp. 20180808, Oct. 2018. [DOI]

Trong-Thuc Hoang, Duc-Hung Le, and Cong-Kha Pham, "VLSI Design of Floating-point Twiddle Factor Using Adaptive CORDIC on Various Iteration Limitations (Invited paper)," in Proc. of IEEE Int. Symp. on Embedded Multicore/Manycore SoCs (MCSoC), Hanoi, Vietnam, Sep. 2018, pp. 225-232. [DOI]

Katsumi Inoue, Trong-Thuc Hoang, Xuan-Thuan Nguyen, Hong-Thu Nguyen, and Cong-Kha Pham, "VLSI Design of Frequent Items Counting Using Binary Decoders Applied to 8-bit per Item Case-study," in Proc. of Conf. on PhD Research in Microelec. and Elec. (PRIME), Prague, Czech Republic, Jul. 2018, pp. 161-164. [DOI]

Trong-Thuc Hoang, Duc-Hung Le, and Cong-Kha Pham, "Minimum Adder-delay Architecture of 8/16/32-point DCT Based on Fixed-rotation Adaptive CORDIC," in IEICE Electronics Express (ELEX), vol. 15, no. 10, pp. 20180302, May 2018. [DOI]

Xuan-Thuan Nguyen, Trong-Thuc Hoang, Hong-Thu Nguyen, Katsumi Inoue, and Cong-Kha Pham, "A 219-μW 1D-to-2D-Based Priority Encoder on 65-nm SOTB CMOS," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Florence, Italy, May 2018, pp. 1-4. [DOI]

Trong-Thuc Hoang, Cong-Kha Pham, and Duc-Hung Le, "High-speed 8/16/32-point DCT Architecture Using Fixed-rotation Adaptive CORDIC," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Florence, Italy, May 2018, pp. 1-5. [DOI]

Katsumi Inoue, Trong-Thuc Hoang, Xuan-Thuan Nguyen, Hong-Thu Nguyen, and Cong-Kha Pham, "High-speed Hardware Implementation of 8-bit per Item Frequent Items Counter," in Proc. of IEEE Symp. on Low-power and High-speed Chips and Syst. (COOLChips), Yokohama, Japan, Apr. 2018, pp. 1-2. [PDF]

Xuan-Thuan Nguyen, Trong-Thuc Hoang, Hong-Thu Nguyen, Katsumi Inoue, and Cong-Kha Pham, "An FPGA-Based Hardware Accelerator for Energy-Efficient Bitmap Index Creation," in IEEE Access, vol. 6, pp. 16046-16059, Mar. 2018. [DOI]

Hong-Thu Nguyen, Xuan-Thuan Nguyen, Trong-Thuc Hoang, and Cong-Kha Pham, "A CORDIC-based QR Decomposition for MIMO Signal Detector," in IEICE Electronics Express (ELEX), vol. 15, no. 6, pp. 20180174, Mar. 2018. [DOI]

2017

Trong-Thuc Hoang, Xuan-Thuan Nguyen, Hong-Thu Nguyen, Nhu-Quynh Truong, Duc-Hung Le, Katsumi Inoue, and Cong-Kha Pham, "FPGA-based Frequent Items Counting Using Matrix of Equality Comparators," in Proc. of IEEE Int. Midwest Symp. on Circ. and Syst. (MWCAS), Boston, USA, Aug. 2017, pp. 285-288. [DOI]

Phuong-Thao Vo-Thi, Trong-Thuc Hoang, Cong-Kha Pham, and Duc-Hung Le, "A Floating-point FFT Twiddle Factor Implementation Based on Adaptive Angle Recoding CORDIC," in Proc. of Int. Conf. on Recent Advances on Signal Processing, Telecomm. & Computing (SigTelCom), Danang, Vietnam, Jan. 2017, pp. 21-26. [DOI]

2016

Trong-Thuc Hoang, Ngoc-Hung Nguyen, and Trong-Tu Bui, "An FPGA-based Implementation of FastICA for Variable-length 4-channel Signal Separation," in Journal of Science & Tech. on Info. and Comm., vol. 1, no. 1, pp. 81–87, 2016. [PDF]

Trong-Thuc Hoang, Hong-Thu Nguyen, Xuan-Thuan Nguyen, Cong-Kha Pham, and Duc-Hung Le, "High-performance DCT Architecture Based on Angle Recoding CORDIC and Scale-free Factor," in Proc. of IEEE Int. Conf. on Comm. and Elec. (ICCE), Halong, Vietnam, Jul. 2016, pp. 199–204. [DOI]

Xuan-Thuan Nguyen, Hong-Thu Nguyen, Trong-Thuc Hoang, Katsumi Inoue, Osamu Shimojo, Toshio Murayama, Kenji Tominaga, and Cong-Kha Pham, "An efficient FPGA-based Database Processor for Fast Database Analytics," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Montreal, Canada, May 2016, pp. 1758–1761. [DOI]

Trong-Thuc Hoang, Duc-Hung Le, Hong-Thu Nguyen, Xuan-Thuan Nguyen, and Cong-Kha Pham, "A Hybrid Adaptive CORDIC in 65nm SOTB CMOS Process," in Proc. of IEEE Int. Symp. on Circ. and Syst. (ISCAS), Montreal, Canada, May 2016, pp. 2158–2161. [DOI]

Hong-Thu Nguyen, Xuan-Thuan Nguyen, Cong-Kha Pham, Trong-Thuc Hoang, and Duc-Hung Le, "A Parallel Pipeline CORDIC Based on Adaptive Angle Selection," in Proc. of Int. Conf. on Elec., Info., and Comm. (ICEIC), Danang, Vietnam, Jan. 2016, pp. 1–4. [DOI]

2015

Xuan-Thuan Nguyen, Hong-Thu Nguyen, Trong-Thuc Hoang, Katsumi Inoue, Osamu Shimojo, Toshio Murayama, Kenji Tominaga, and Cong-Kha Pham, "Database Processor (DBP) - A New Search Engine for the Big Data Era," in Proc. of IEICE Int. Conf. on Integrated Circ. and Devices in Vietnam (ICDV), Hochiminh city, Vietnam, 2015, pp. 9-14. [PDF]

Hong-Thu Nguyen, Xuan-Thuan Nguyen, Cong-Kha Pham, Trong-Thuc Hoang, and Duc-Hung Le, "A Low-resource Low-latency Hybrid Adaptive CORDIC in 180-nm CMOS Technology," in Proc. of IEEE Region 10 Conf. (TENCON), Singapore, Singapore, Nov. 2015, pp. 1–4. [DOI]

Trong-Thuc Hoang, Hong-Kiet Su, Hieu-Binh Nguyen, Duc-Hung Le, Huu-Thuan Huynh, Trong-Tu Bui, and Cong-Kha Pham, "Design of Co-processor for Real-time HMM-based Text-to-speech on Hardware System Applied to Vietnamese," in IEICE Electronics Express (ELEX), vol. 12, no. 14, pp. 20150448, Jul. 2015. [DOI]

Hong-Thu Nguyen, Xuan-Thuan Nguyen, Trong-Thuc Hoang, Duc-Hung Le, and Cong-Kha Pham, "Low-resource Low-latency Hybrid Adaptive CORDIC with Floating-point Precision," in IEICE Electronics Express (ELEX), vol. 12, no. 9, pp. 20150258, May 2015. [DOI]

2014

Dinh-Thien Vu, Trong-Thuc Hoang, Ngoc-Hung Nguyen, and Trong-Tu Bui, "An FPGA-based Variable-length 4-Channel Separation FastICA Implementation," in Proc. of IEICE Int. Conf. on Integrated Circ. and Devices in Vietnam (ICDV), Hanoi, Vietnam, Nov. 2014, pp. 141-146. [PDF]

Xuan-Vy Luu, Trong-Thuc Hoang, Trong-Tu Bui, and Anh-Vu Dinh-Duc, "A High-speed Unsigned 32-bit Multiplier Based on Booth-encoder and Wallace-tree Modifications," in Proc. of Int. Conf. on Advanced Tech. for Comm. (ATC), Hanoi, Vietnam, Oct. 2014, pp. 739–744. [DOI]

Trong-Thuc Hoang, Quang-Trung Tran, and Trong-Tu Bui, "A Proposed Adaptive Image Segmentation Method Based on Local Excitatory Global Inhibitory Region Growing," in Proc. of IEEE Int. Conf. on Comm. and Elec. (ICCE), Danang, Vietnam, Jul. 2014, pp. 458–463. [DOI]

Đàm Quang Linh, Hoàng Trọng Thức, Bùi Trọng Tú, and Đinh-Đức Anh-Vũ, "Hiện Thực và So Sánh các Thiết Kế FFT 2048 Điểm Xây Dựng trên Nền Tảng FPGA," in Proc. of Hội Thảo Quốc Gia về Điện Tử, Truyền Thông, và Công Nghệ Thông Tin (REV-ECIT), Nhatrang, Vietnam, 2014, pp. 260–265. [PDF]

2013

Thai-Bao Huynh, Trong-Thuc Hoang, and Trong-Tu Bui, "A Constraint-based Watermarking Technique Using Schmitt Trigger Insertion at Logic Synthesis Level," in Proc. of Int. Conf. on Advanced Tech. for Comm. (ATC), Hochiminh city, Vietnam, Oct. 2013, pp. 115–120. [DOI]

Kim-Hung Nguyen, Trong-Thuc Hoang, and Trong-Tu Bui, "An FSM-based IP Protection Technique Using Added Watermarked States," in Proc. of Int. Conf. on Advanced Tech. for Comm. (ATC), Hochiminh city, Vietnam, Oct. 2013, pp. 718–723. [DOI]

2012

Trong-Thuc Hoang, Vi-Thuy Tran, Thanh Le, Minh-Triet Luu, Cao-Quyen Tran, Xuan-Thuan Nguyen, and Trong-Tu Bui, "A Case Study of Connect6 Game FPGA-based Implementation Using the Multi-turn Prediction Algorithm," in Proc. of IEEE Int. Symp. on Signal Processing and Info. Tech. (ISSPIT), Hochiminh city, Vietnam, Dec. 2012, pp. 1-6. [PDF]

Trong-Thuc Hoang, Ngoc-Hung Nguyen, Xuan-Thuan Nguyen, and Trong-Tu Bui, "A Real-time Object-recognition System Based on PCNN Algorithm," in Proc. of IEICE Int. Conf. on Integrated Circ. and Devices in Vietnam (ICDV), no. 2, Danang, Vietnam, Aug. 2012, pp. 155–160. [PDF]