RISC-V Chip Collection

IV. Crypto Processor (CryPro) Chips

IV.1) CryPro Single-core Rocket-chip with TLS-1.3 Compatible Crypto-cores

Summary

| Process | ROHM-180nm |

| Die | 5×5-mm2 |

| Fab. Date | Feb. 2022 |

| ISA | RV32IMAC |

| Core | Rocket (×1) |

| Cryptography Accelerator | AES-GCM, ChaCha20, Poly1305, AEAD, Ed/EC-DSA, HMAC-SHA2, RSA-1024, SHA3-512, and TRNG |

| Secure Boot | MCU as sub-system with IBex core (RV32IMC) |

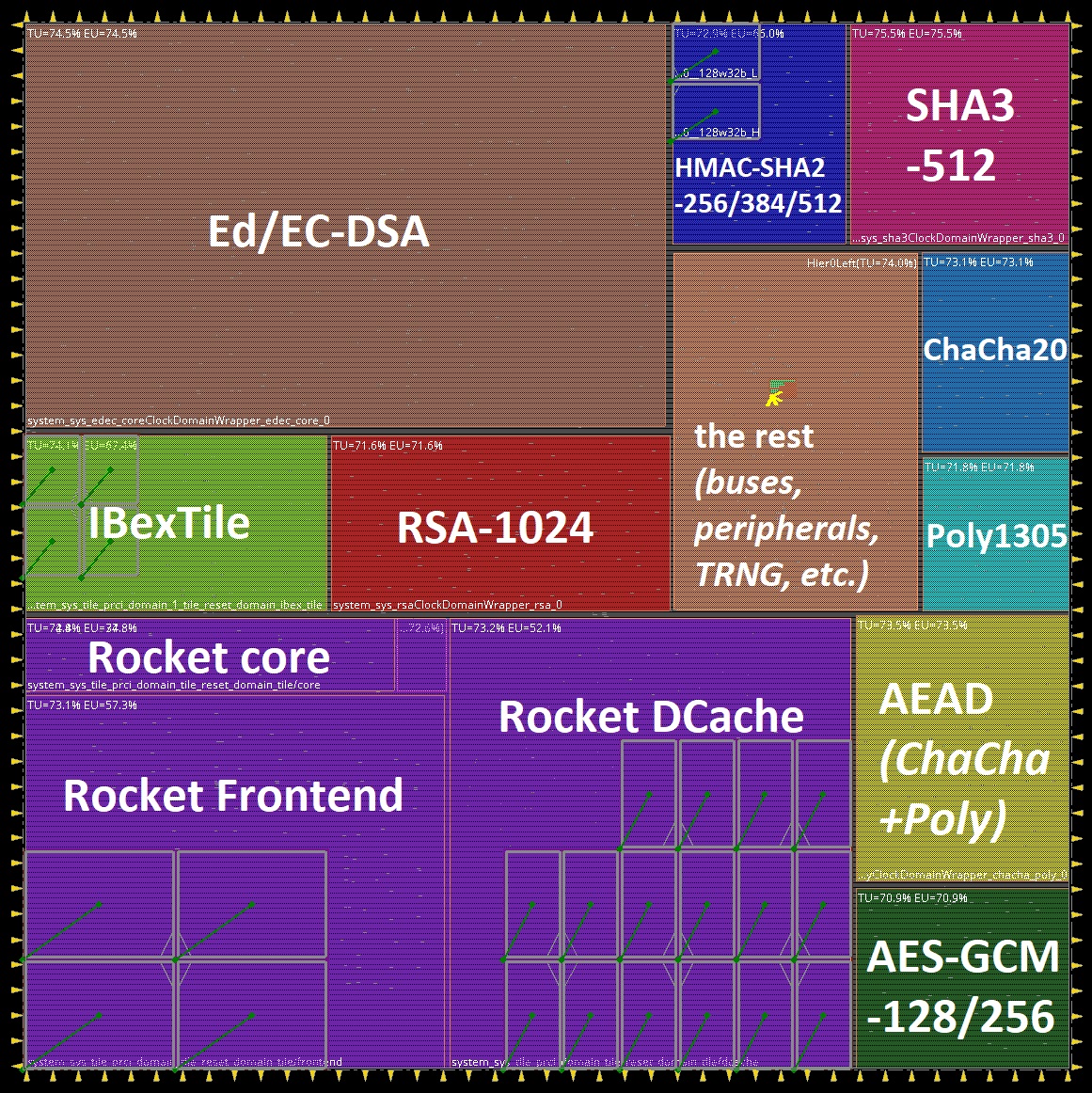

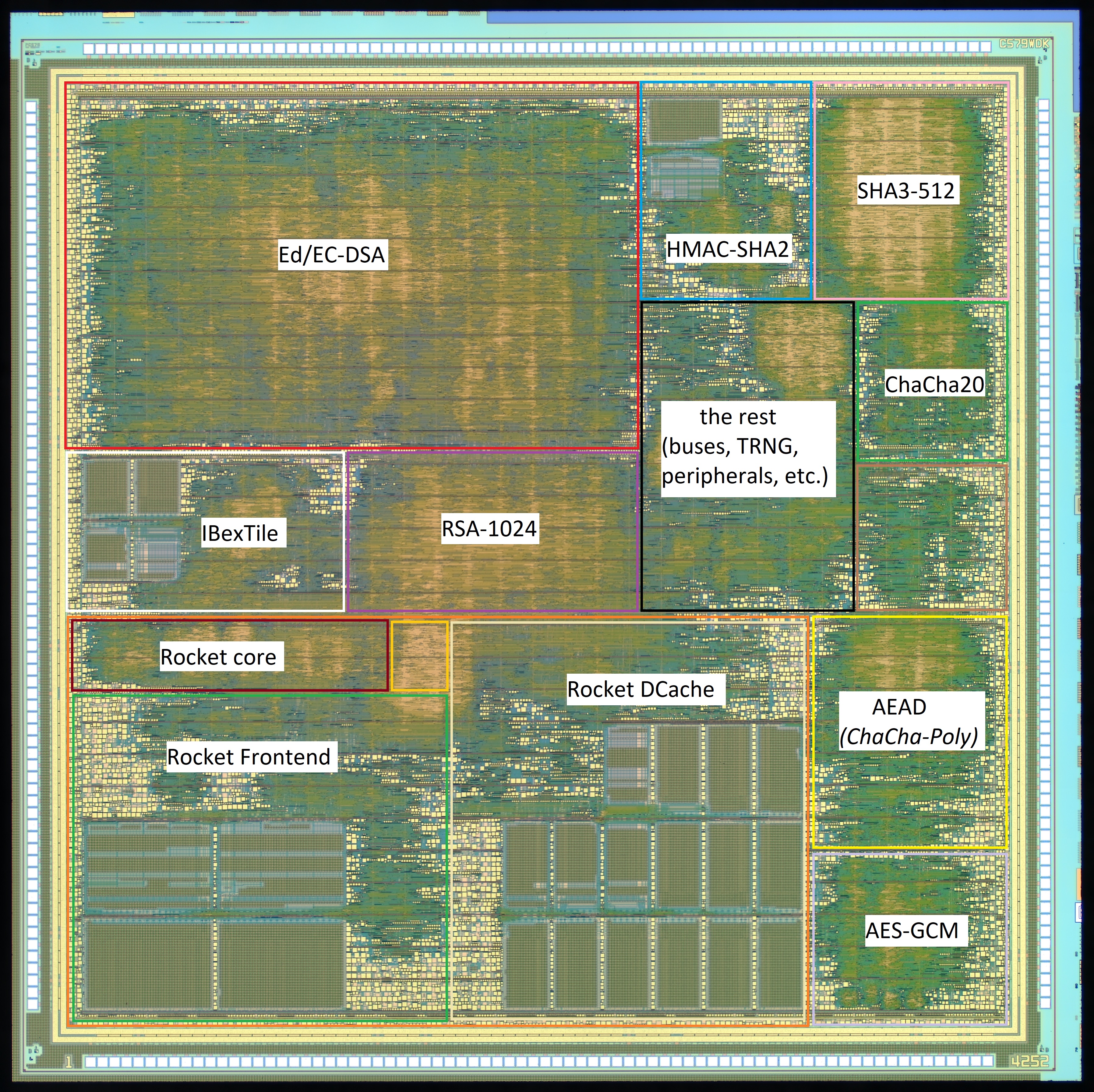

Floorplan

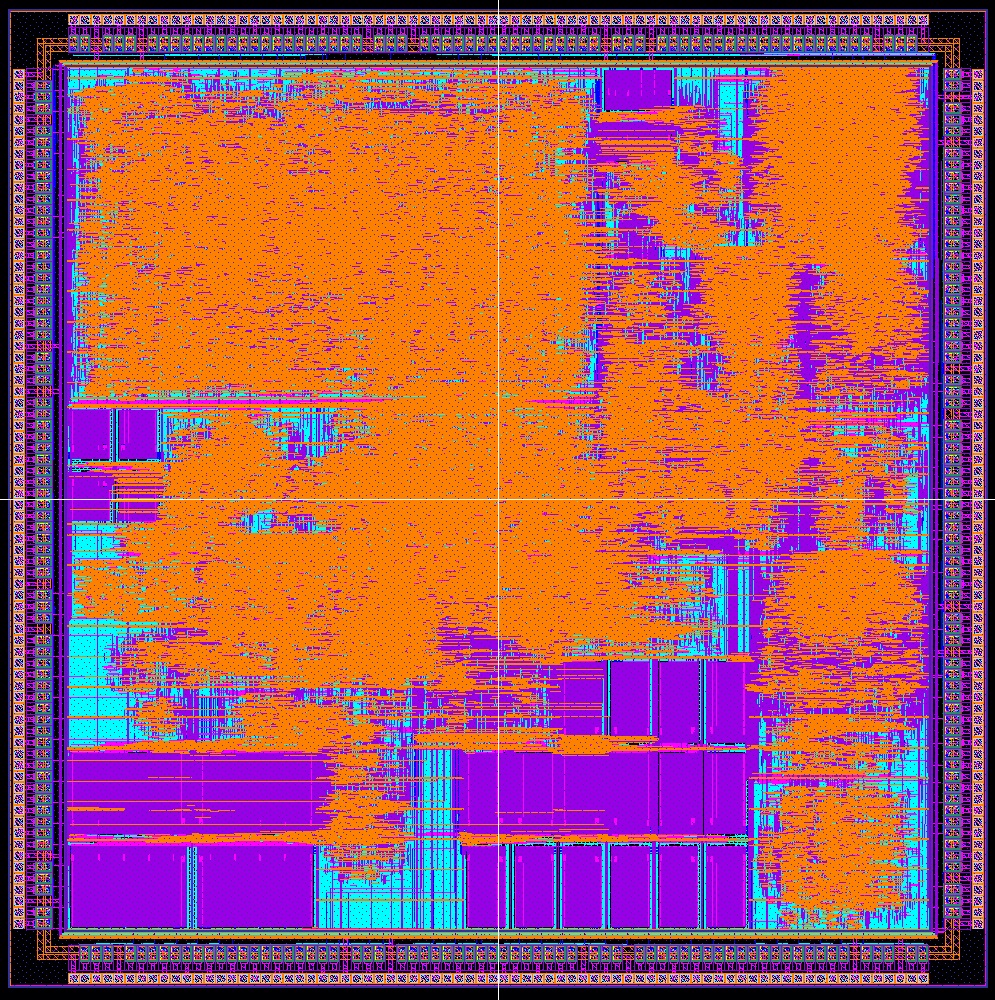

Layout

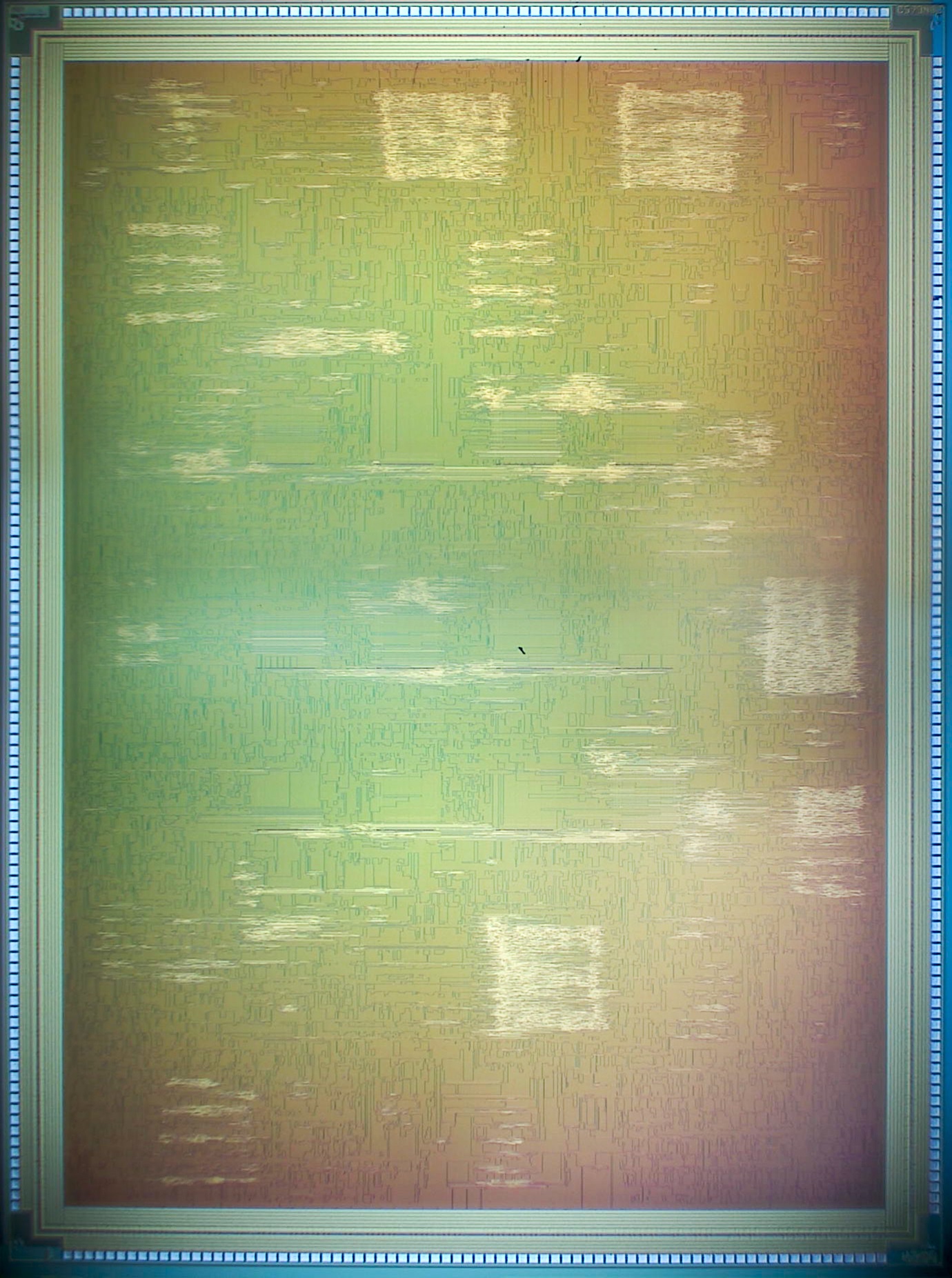

Barechip

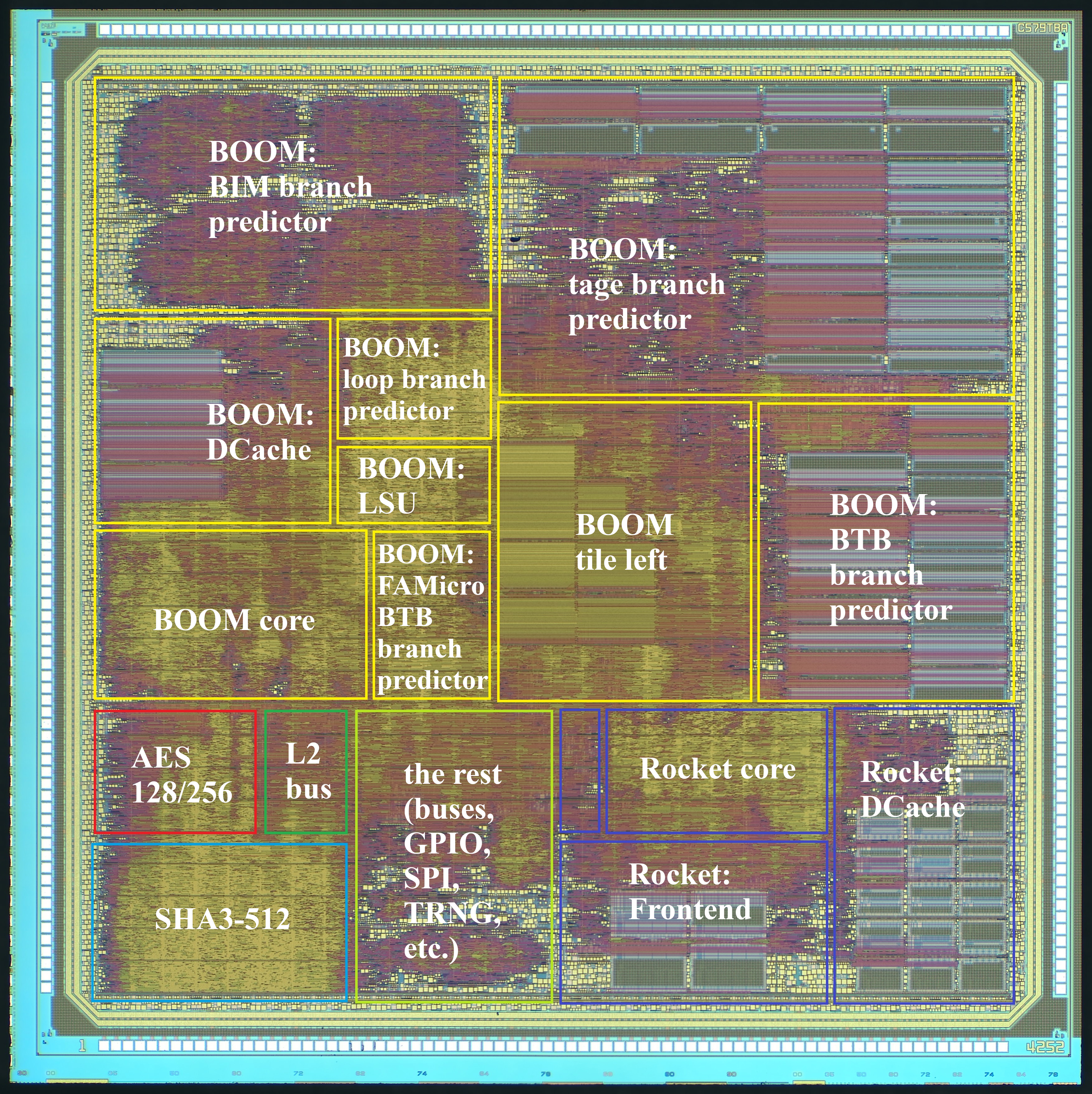

III. Trusted Execution Environment (TEE) Hardware Chips

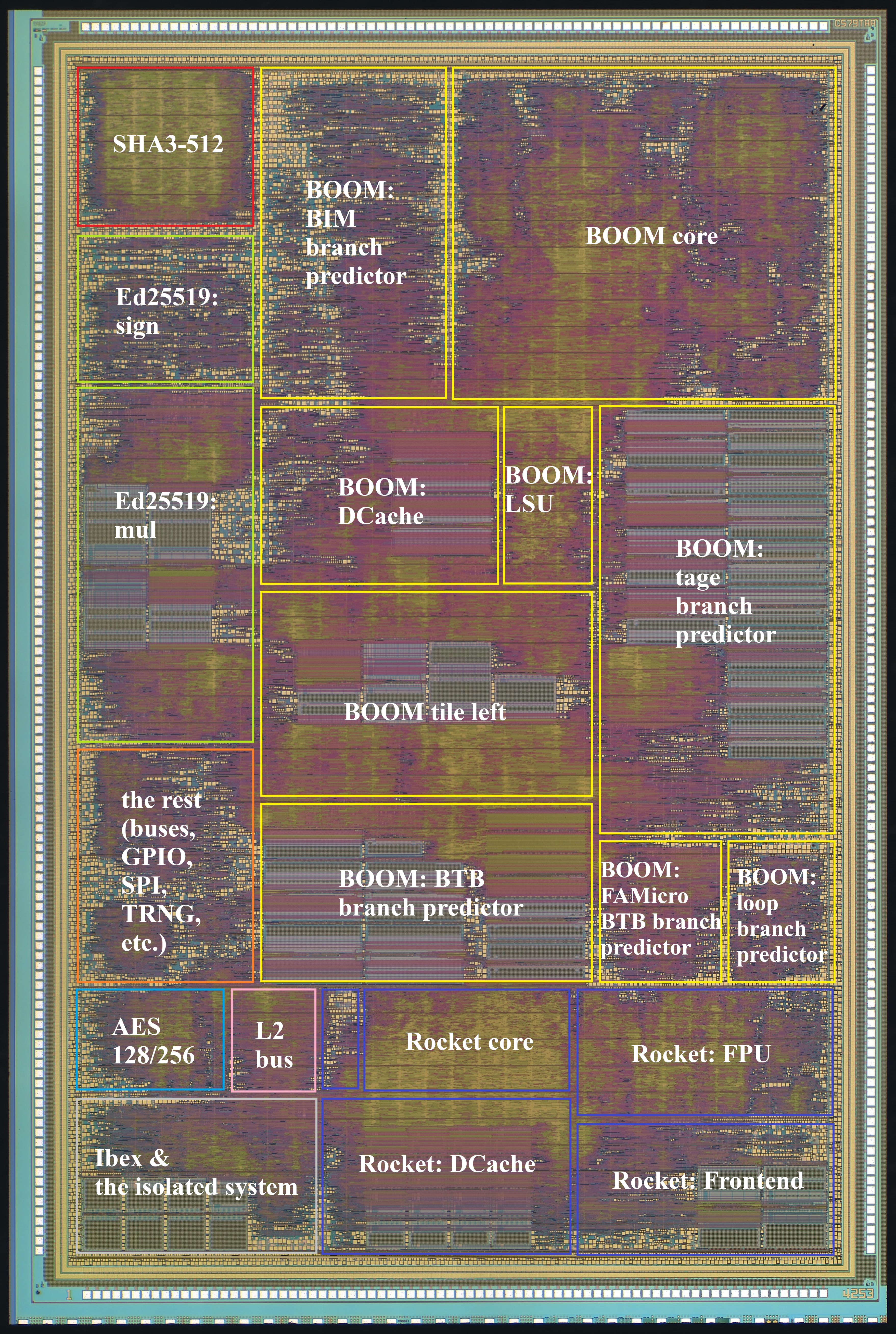

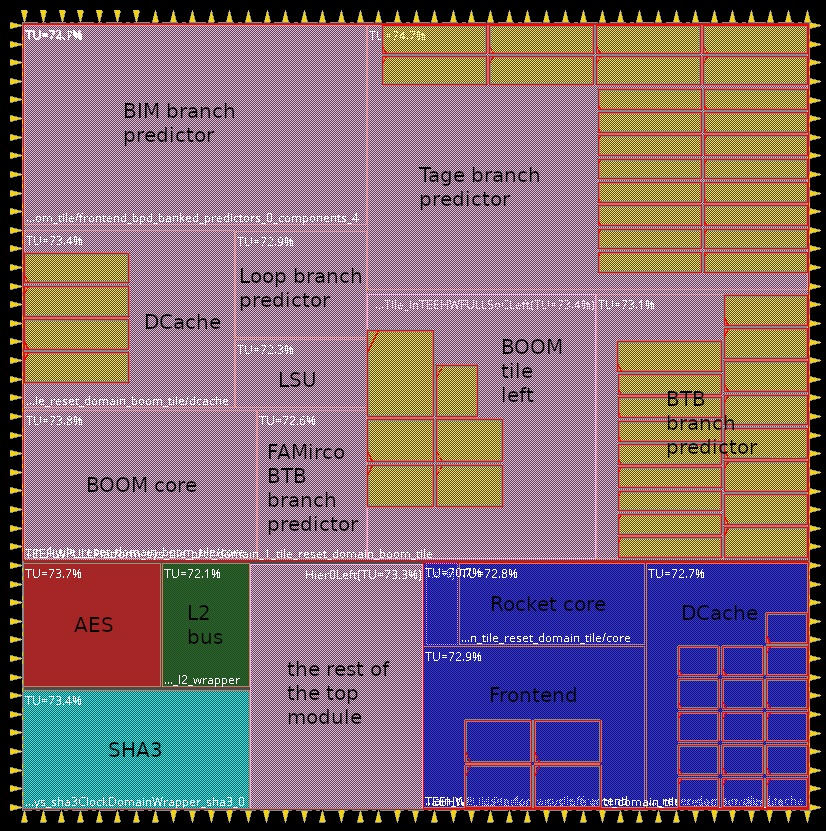

III.6) TEEHW 64-bit Dual-core Rocket-Boom with Secure Boot Sub-system, Crypto-cores, and TRNG

Summary

| Process | ROHM-180nm |

| Die | 5×7.5-mm2 |

| Fab. Date | Jun. 2021 |

| ISA | RV64GC |

| Core | Rocket (×1) + Boom (×1) |

| Cryptography Accelerator | AES, SHA3-512, Ed25519, and TRNG |

| Secure Boot | MCU as sub-system with IBex core (RV32IMC) |

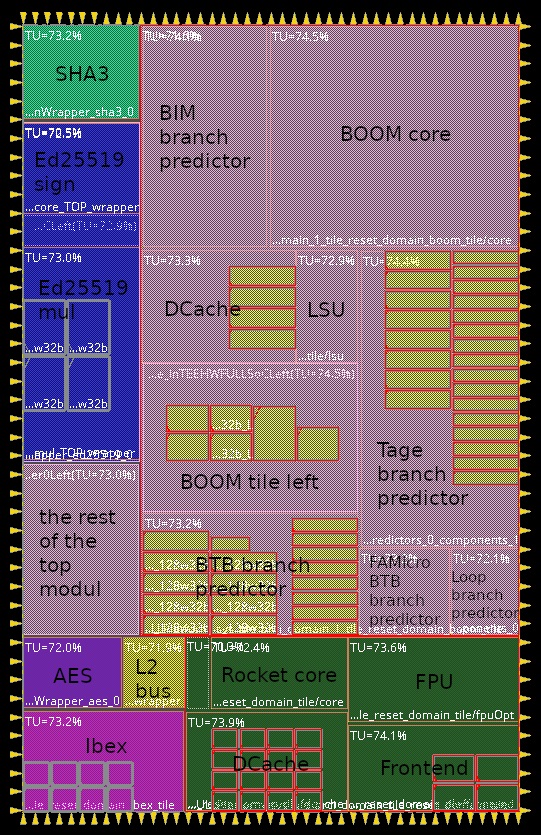

Floorplan

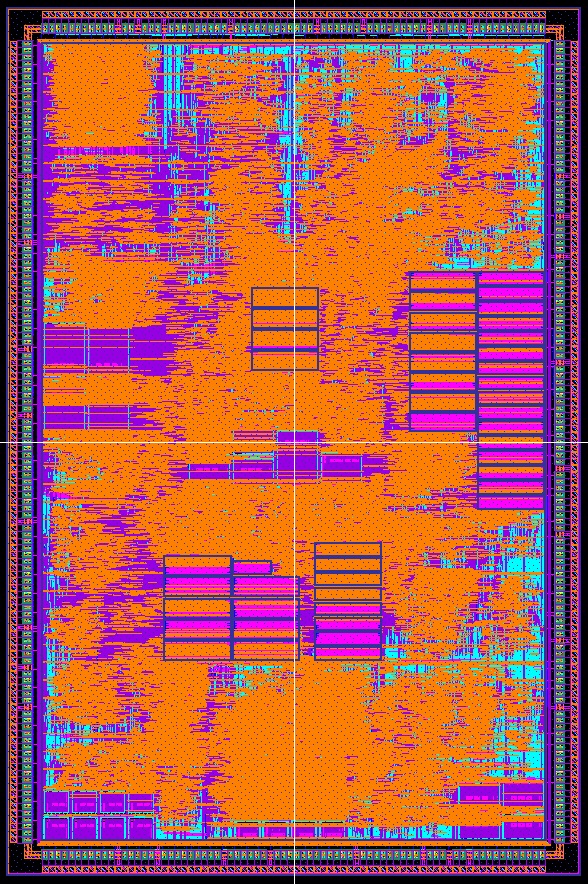

Layout

Barechip

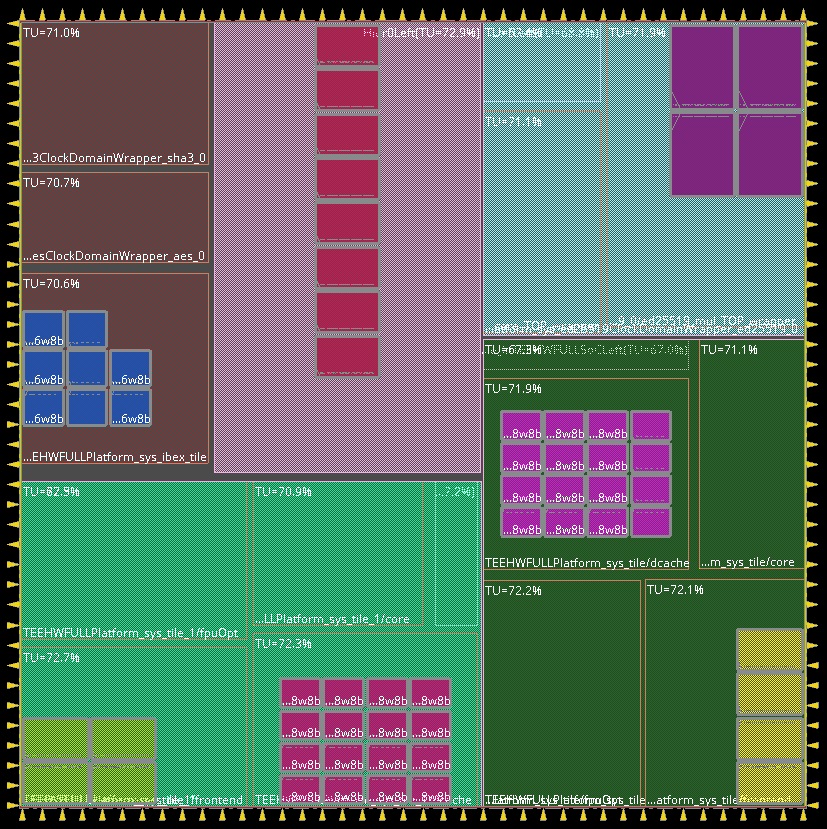

III.5) TEEHW 32-bit Dual-core Rocket-Boom with Secure Boot Sub-system, Crypto-cores, and TRNG

Summary

| Process | ROHM-180nm |

| Die | 5×5-mm2 |

| Fab. Date | Jun. 2021 |

| ISA | RV32IMAC |

| Core | Rocket (×1) + Boom (×1) |

| Cryptography Accelerator | AES, SHA3-512, and TRNG |

| Secure Boot | MCU as sub-system with IBex core (RV32IMC) |

Floorplan

Layout

Barechip

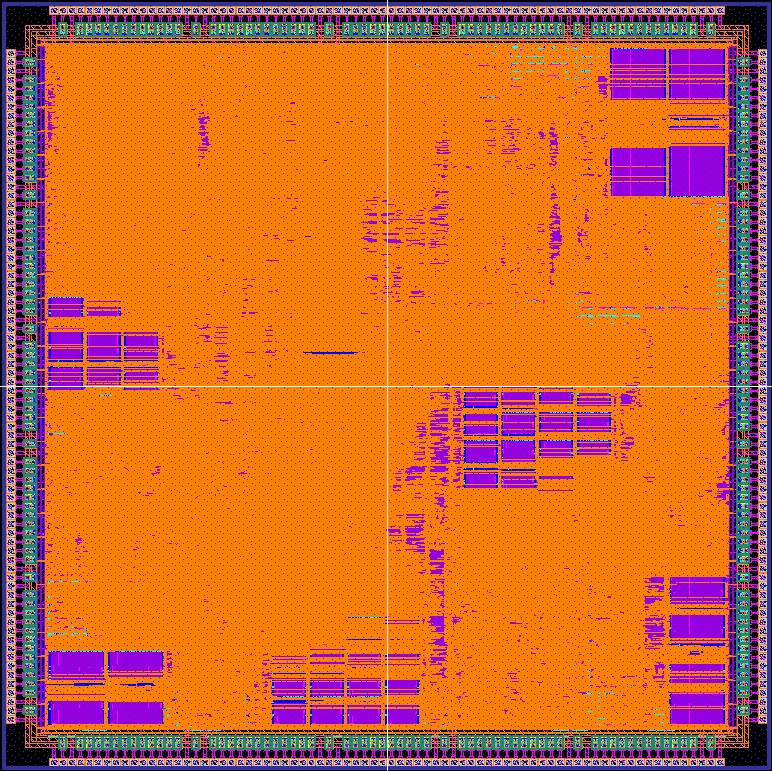

III.4) TEEHW 64-bit Dual-core Rocket-chip with Crypto-cores and TRNG

Summary

| Process | ROHM-180nm |

| Die | 5×5-mm2 |

| Fab. Date | Feb. 2021 |

| ISA | RV64GC |

| Core | Rocket (×2) |

| Cryptography Accelerator | AES, SHA3-512, Ed25519, and TRNG |

| Secure Boot | MCU as sub-system with IBex core (RV32IMC) |

Floorplan

Layout

Barechip

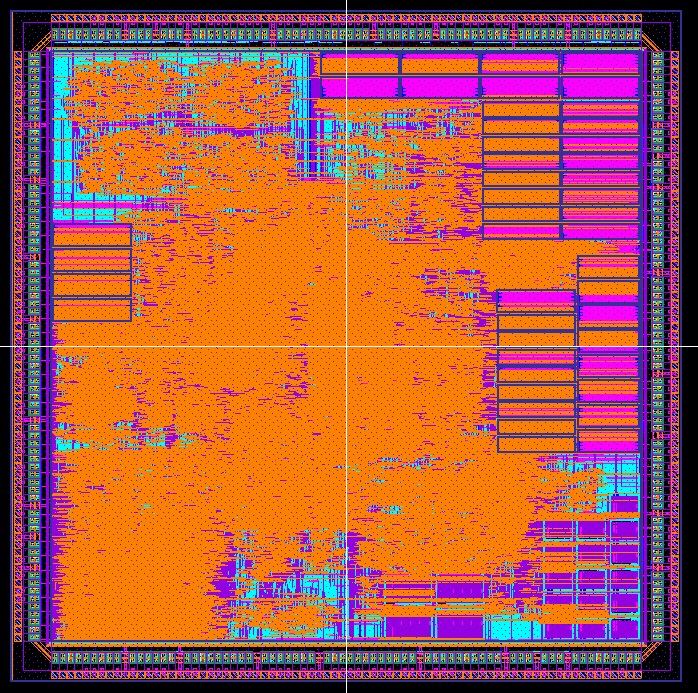

III.3) TEEHW 64-bit Single-core Boom with Crypto-cores

Summary

| Process | ROHM-180nm |

| Die | 5×5-mm2 |

| Fab. Date | Jun. 2020 |

| ISA | RV64GC |

| Core | Boom (×1) |

| Cryptography Accelerator | AES, SHA3-512, and Ed25519 |

Layout

Barechip

III.2) TEEHW 32-bit Dual-core Rocket-Boom with Crypto-cores

Summary

| Process | ROHM-180nm |

| Die | 5×5-mm2 |

| Fab. Date | Jun. 2020 |

| ISA | RV32IMAC |

| Core | Rocket (×1) + Boom (×1) |

| Cryptography Accelerator | AES, SHA3-512, and Ed25519 |

Layout

Barechip

III.1) TEEHW 64-bit Dual-core Rocket-chip with Crypto-cores

Summary

| Process | ROHM-180nm |

| Die | 5×5-mm2 |

| Fab. Date | Jan. 2020 |

| ISA | RV64GC |

| Core | Rocket (×2) |

| Cryptography Accelerator | AES, SHA3-512, and Ed25519 |

Layout

Barechip

II. VexRiscv Chips

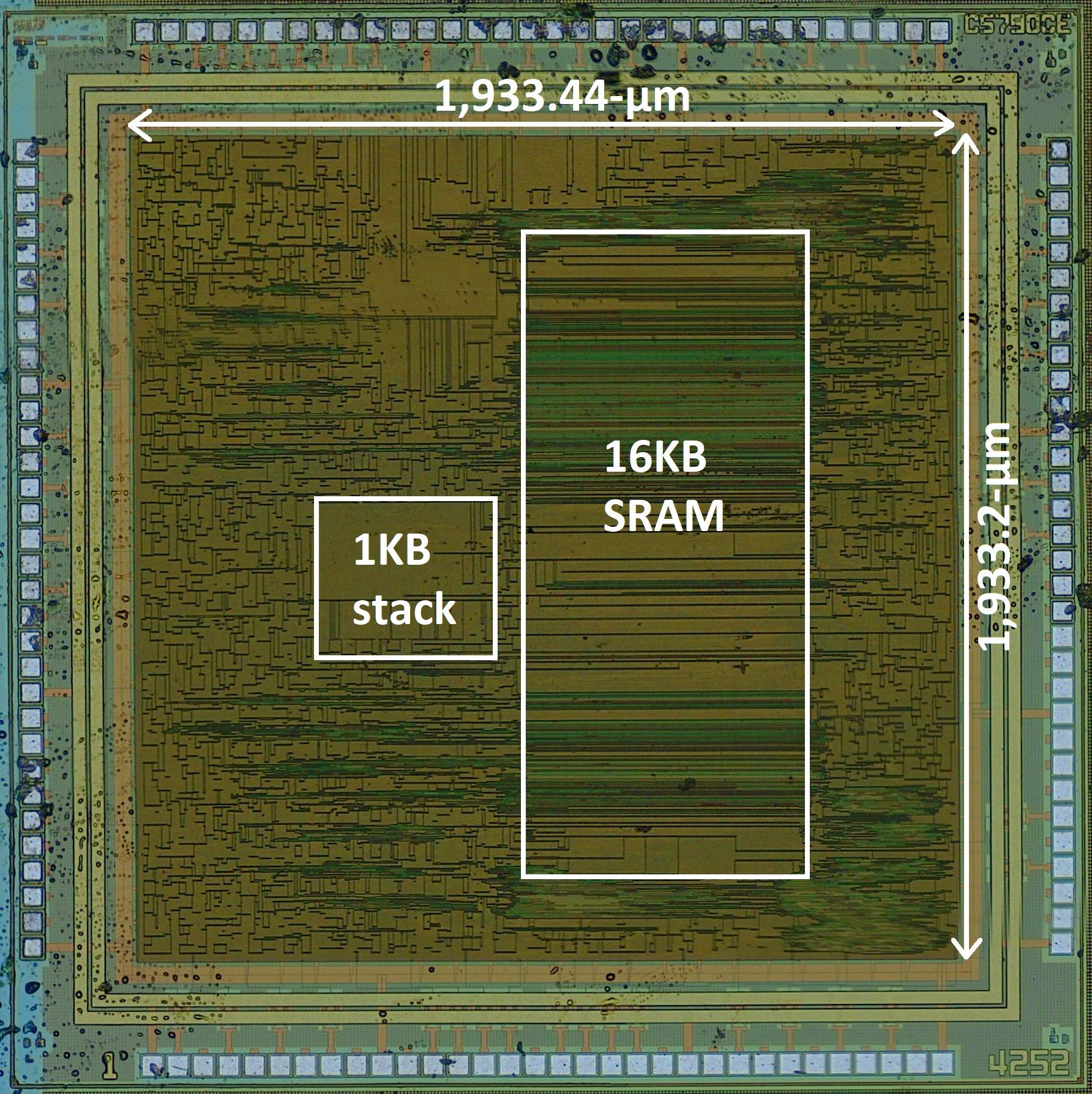

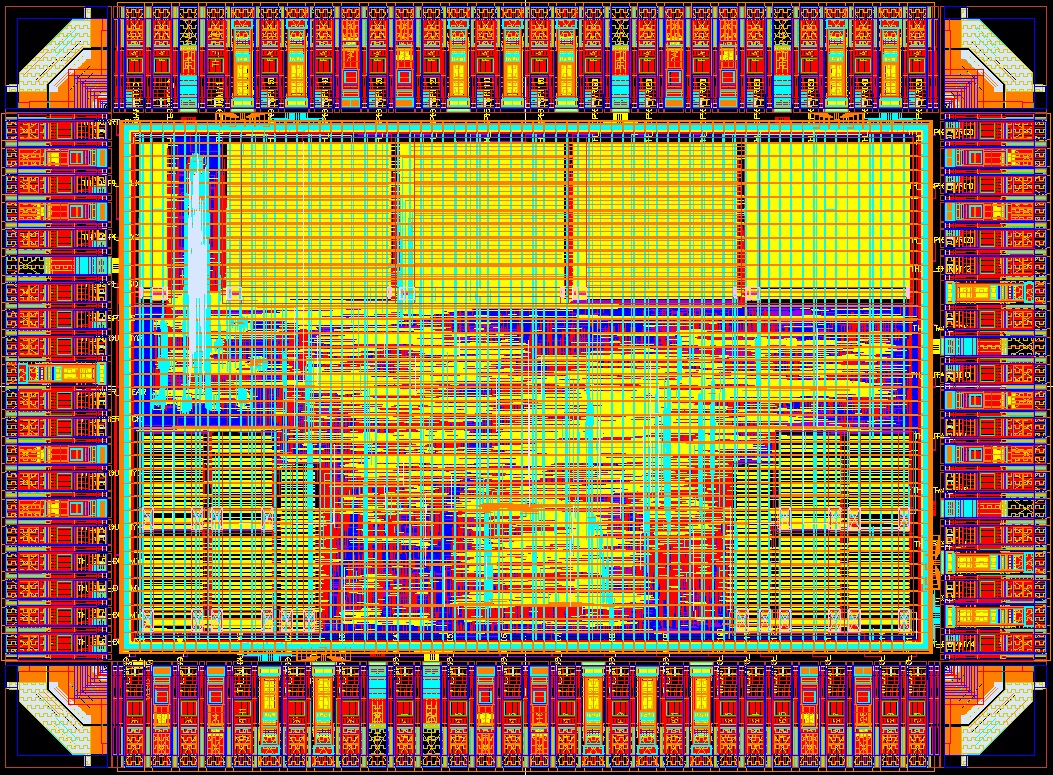

II.2) VexRiscv ROHM Chip

Summary

| Process | ROHM-180nm |

| Die | 2.5×2.5-mm2 |

| Fab. Date | Jan. 2020 |

| ISA | RV32IM |

| Core | VexRiscv (×1) |

Layout

Barechip

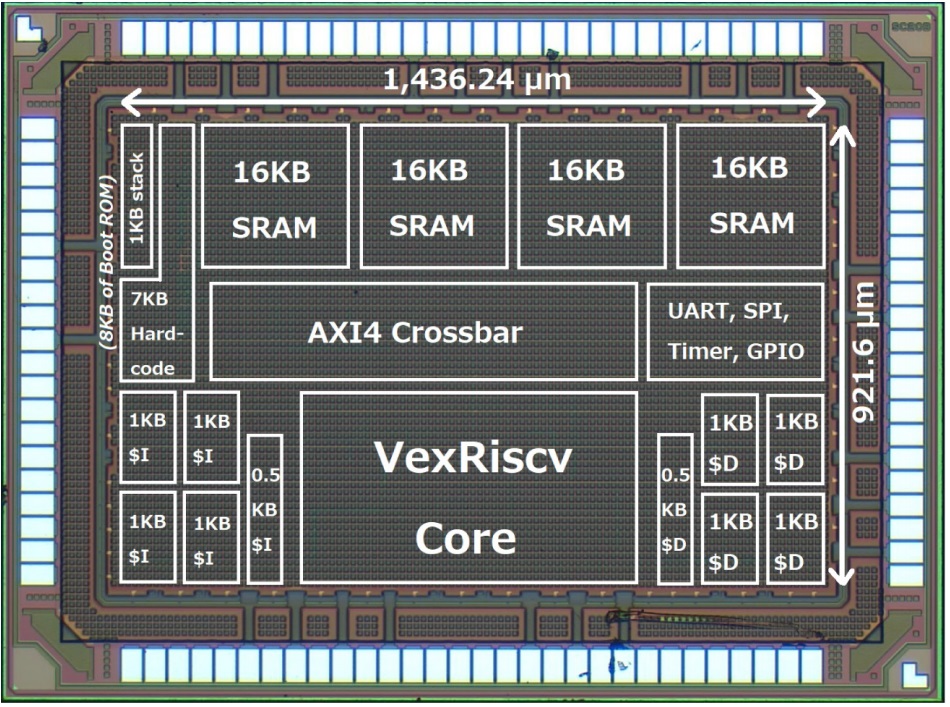

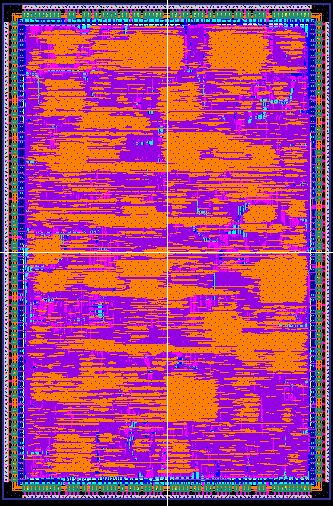

II.1) VexRiscv SOTB Chip

Summary

| Process | SOTB-65nm |

| Die | 2×1.5-mm2 |

| Fab. Date | Aug. 2019 |

| ISA | RV32IM |

| Core | VexRiscv (×1) |

Layout

Barechip

I. Freedom Chips

I.1) Freedom Quad-core Rocket-chip

Summary

| Process | ROHM-180nm |

| Die | 5×7.5-mm2 |

| Fab. Date | Oct. 2019 |

| ISA | RV64GC |

| Core | Rocket (×4) |

Layout

Barechip